設(she)計(ji)方(fang)案(an)

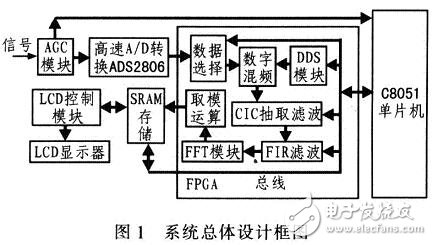

圖1為(wei)系(xi)統(tong)設(she)計(ji)總(zong)體框圖。該(gai)系統(tong)采(cai)用(yong)C8051($8.5125)系(xi)列(lie)單片機(ji)中(zhong)的(de) C8051($8.5125)F121作為(wei)控制(zhi)器,CvcloneⅢ系列(lie)EP3C40F484C8($86.5000)型(xing)FPGA為(wei)數(shu)字(zi)信號算(suan)法處理(li)單元(yuan)。系統(tong)設(she)計(ji)遵(zun)循抽(chou)樣定理(li),在(zai)時域(yu)內(nei)截(jie)取壹(yi)段適(shi)當(dang)長度信號,對其(qi)信號抽樣(yang)量化(hua),按(an)照(zhao)具體(ti)的(de)步(bu)驟(zhou)求(qiu)取信號的頻譜,並(bing)在(zai)LCD上(shang)顯示(shi)信號的頻譜,同時提(ti)供(gong)友(you)好(hao)的(de)人(ren)機會(hui)話(hua)功能。該(gai)系統(tong)zui小分辨(bian)率(lv)為(wei)1 Hz,可(ke)分(fen)析(xi)帶(dai)寬(kuan)為(wei)0~5 MHz的(de)各種(zhong)信號。

由於(yu)單片機(ji)C8051($8.5125) F121內(nei)部(bu)集(ji)成A/D轉換器,能夠(gou)有(you)效(xiao)測量自(zi)動(dong)增益控制(zhi)AGC壓差,計(ji)算(suan)出對(dui)輸入(ru)信號的放(fang)大倍數;另(ling)外(wai),該(gai)單片機(ji)內(nei)置高速控制(zhi)內(nei)核(he)和(he)豐富的(de)存儲器,使其(qi)能夠(gou)控制(zhi)整(zheng)個系統(tong);EP3C40F484C8($86.5000)型(xing)FPGA內(nei)置豐富的(de)存儲器資源(yuan),確(que)保該(gai)系統(tong)具有(you)足(zu)夠(gou)的(de)空(kong)間(jian)存(cun)儲(chu)采(cai)集(ji)的點(dian)數(shu),完成離(li)散(san)傅裏(li)葉(ye)變(bian)換(huan)、數字濾波(bo)器、數字(zi)混(hun)頻等(deng)信號處理(li)。

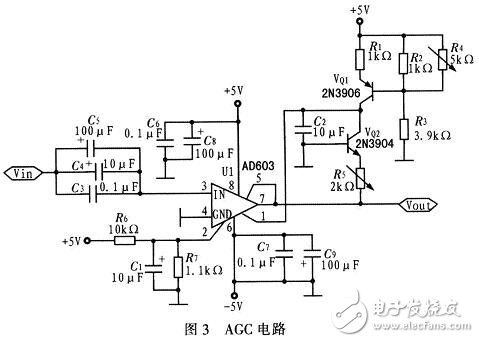

AGC電路(lu)

輸入(ru)信號經高(gao)速A/D采(cai)樣(yang),信號幅度必須滿足(zu)A/D的采(cai)樣(yang)範圍,zui高(gao)為(wei)2-3V,因(yin)此(ci)該(gai)系統(tong)設(she)計(ji)應加(jia)AGC電路(lu)。AGC電路(lu)采(cai)用(yong)AD603($6.4440)型(xing)線(xian)性(xing)增益放大器。圖3為(wei)AGC電路(lu)。

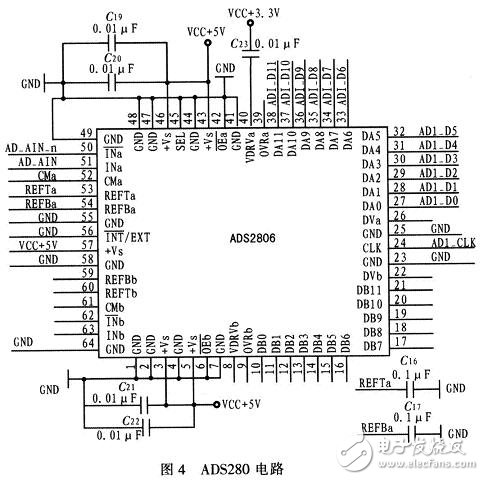

A/D轉換電路(lu)

ADS2806($21.5437)是壹(yi)款12位(wei)A/D轉換器,其特(te)點(dian)為(wei):無(wu)雜散(san)信號動(dong)態範(fan)圍(SFDR)為(wei)73 dB;信噪比(SNR)為(wei)66 dB;具有(you)內(nei)部(bu)和(he)外(wai)部(bu)參(can)考(kao)時(shi)鐘(zhong);采(cai)樣(yang)速率(lv)為(wei)32 MS/s。圖4為(wei)ADS2806($21.5437)的(de)電路(lu)。為(wei)使(shi)A/D轉換更(geng)穩(wen)定(ding),在(zai)A/D轉換器的電源(yuan)引(yin)腳(jiao)上(shang)增加(jia)濾(lv)波(bo)電容(rong),抑(yi)制(zhi)電源(yuan)噪聲。該(gai)電路(lu)結(jie)構(gou)簡(jian)單,在時(shi)鐘(zhong)CLK的(de)驅(qu)動(dong)下,數(shu)據端(duan)口(kou)實時輸出(chu)數(shu)據,供(gong)FPGA讀(du)取。

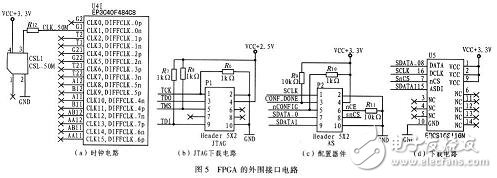

FPGA及外(wai)圍接口(kou)模(mo)塊(kuai)

選(xuan)用(yong)Cyclone($898.9000)Ⅲ系(xi)列(lie) EP3C40F484($86.5000)型(xing)FPGA,該(gai)器件內(nei)部(bu)有39 600個LE資源(yuan),有(you)1 134 000 bit的存儲(chu)器,同時還有126個乘(cheng)法器和(he)4個PLL鎖相環。由於(yu)該(gai)器件內(nei)部(bu)有大量(liang)資源(yuan),因(yin)而(er)可(ke)滿足(zu)其內(nei)部(bu)實現(xian)數字混(hun)頻、數字濾(lv)波(bo)、以及(ji)FFT運算(suan)。FP -GA正常(chang)工作時,主(zhu)要需要的外(wai)部(bu)接口(kou)有:時鐘(zhong)電路(lu)、JTAG下載(zai)電路(lu)、配(pei)置器件及下(xia)載(zai)電路(lu)。圖5為(wei)FPGA的(de)外(wai)圍接口(kou)電路(lu)。

該(gai)系統(tong)能夠(gou)方(fang)便(bian)地(di)在LCD上(shang)顯示(shi)信號的頻譜結(jie)構(gou)圖。操(cao)作簡單,非(fei)常(chang)適(shi)合教(jiao)學(xue)實驗室(shi)學(xue)生使用(yong)。

文(wen)章(zhang)來(lai)源(yuan):電子發燒友(you)

上(shang)壹(yi)篇:實(shi)時頻譜分析(xi)儀工(gong)作原(yuan)理(li)

下(xia)壹(yi)篇:電動(dong)汽車(che)充(chong)電樁(zhuang)電子測(ce)試項目(mu)

返(fan)回列(lie)表 | 返(fan)回頂(ding)部(bu)

會(hui)員_a.png)